FPGA |

您所在的位置:网站首页 › i2c ack没应答 › FPGA |

FPGA

|

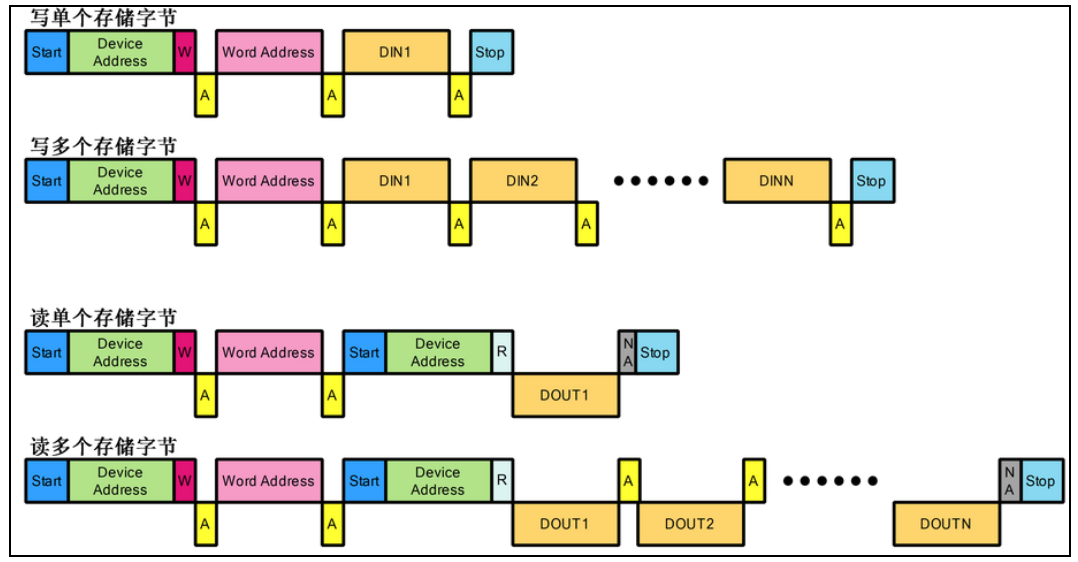

IIC 的总线协议和时序IIC 标准速率为 100kbit/s,快速模式 400kbit/s,支持多机通讯, 支持多主控模块,但同一时刻只允许有一个主控。 由数据线 SDA 和时钟 SCL 构成串行总线;每个电路和模块都有唯一的地址。 在这里以 AT24C04 为例说明 I2C 读写的基本操作和时序,I2C 设备的操作可分为写单个存储字节,写多个存储字节,读单个存储字节和读多个存储字节。 各个操作如下图所示。

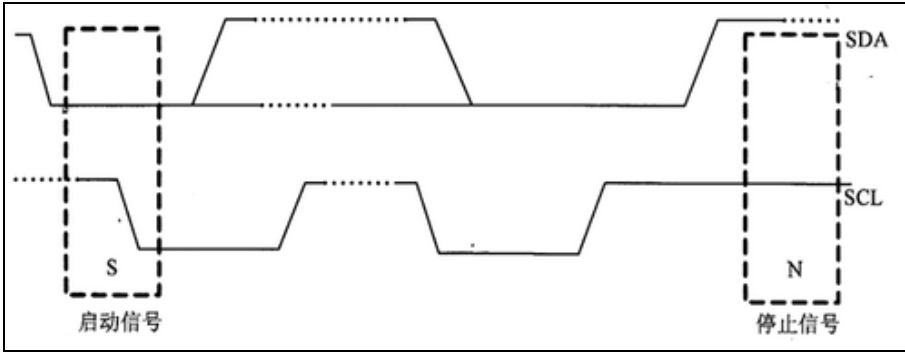

下面对 I2C 总线通信过程中出现的几种信号状态和时序进行分析。①总线空闲状态I2C 总线总线的 SDA 和 SCL 两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。②启动信号(Start)在时钟线 SCL 保持高电平期间,数据线 SDA 上的电平被拉低(即负跳变),定义为 I2C 总线 总线的启动信号,它标志着一次数据传输的开始。启动信号是由主控器主动建立的,在建立该信号之前 I2C 总线必须处于空闲状态,如下图所示。

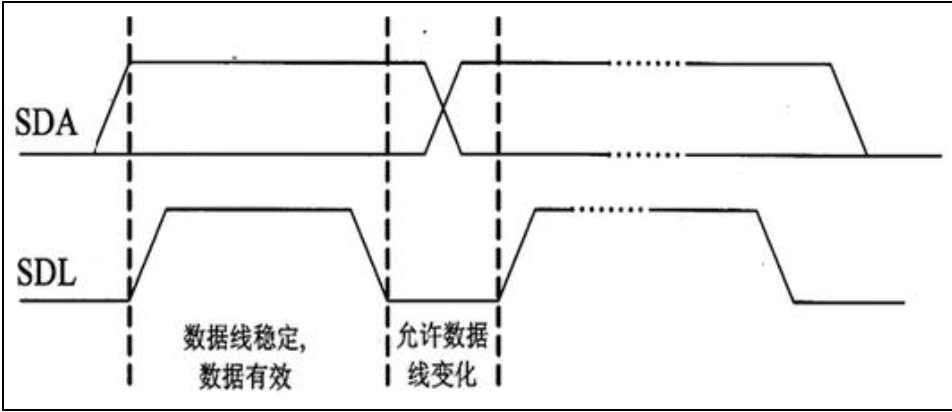

③停止信号(Stop)在时钟线 SCL 保持高电平期间,数据线 SDA 被释放,使得 SDA 返回高电平(即正跳变),称为 I2C 总线的停止信号,它标志着一次数据传输的终止。停止信号也是由主控器主动建立的,建立该信号之后,I2C 总线将返回空闲状态。 ④数据位传送在 I2C 总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在 SCL 串行时钟的配合下,在 SDA 上逐位地串行传送每一位数据。进行数据传送时,在 SCL 呈现高电平期间,SDA 上的电平必须保持稳定,低电平为数据 0,高电平为数据 1。只有在 SCL 为低电平期间,才允许 SDA 上的电平改变状态。

⑤应答信号(ACK 和 NACK)I2C 总线上的所有数据都是以 8 位字节传送的,发送器每发送一个字节,就在时钟脉冲 9 期间释放数据线,由接收器反馈一个应答信号。应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。对

于反馈有效应答位 ACK 的要求是,接收器在第 9 个时钟脉冲之前的低电平期间将 SDA 线拉低,并且确保在该时钟的高电平期间为稳定的低电平。如果接收器是主控器,则在它收到最后一个字节后,发送一个 NACK 信号,以通知被控发送器结束数据发送,并释放 SDA 线,以便主控接收器发送一个停止信号。

1. 编写 IIC 的通信程序 iic_com.v module iic_com ( input CLK, input RSTn, input [1:0] Start_Sig, //read or write command input [7:0] Addr_Sig, //eeprom words address input [7:0] WrData, //eeprom write data output [7:0] RdData, //eeprom read data output Done_Sig, //eeprom read/write finish output SCL, inout SDA ); parameter F100K = 9'd500; //100Khz的时钟分频系数 reg [4:0]i; reg [4:0]Go; reg [9:0]C1; reg [7:0]rData; reg rSCL; reg rSDA; reg isAck; reg isDone; reg isOut; assign Done_Sig = isDone; assign RdData = rData; assign SCL = rSCL; assign SDA = isOut ? rSDA : 1'bz; //SDA数据输出选择 //****************************************// //* I2C读写处理程序 *// //****************************************// always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) begin i |

【本文地址】

今日新闻 |

推荐新闻 |